## Interface studies of GaAs metal-oxide-semiconductor structures using atomic-layer-deposited HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate gate dielectric

T. Yang, Y. Xuan, D. Zemlyanov, T. Shen, Y. Q. Wu, J. M. Woodall, and P. D. Ye<sup>a)</sup> School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

F. S. Aguirre-Tostado, M. Milojevic, S. McDonnell, and R. M. Wallace *Materials Science and Engineering, University of Texas at Dallas, Richardson, Texas 75083, USA*

(Received 1 August 2007; accepted 21 September 2007; published online 5 October 2007)

A systematic capacitance-voltage study has been performed on GaAs metal-oxide-semiconductor (MOS) structures with atomic-layer-deposited HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminates as gate dielectrics. A HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate gate dielectric improves the GaAs MOS characteristics such as dielectric constant, breakdown voltage, and frequency dispersion. A possible origin for the widely observed larger frequency dispersion on *n*-type GaAs than *p*-type GaAs is discussed. Further experiments show that the observed hysteresis is mainly from the mobile changes and traps induced by HfO<sub>2</sub> in bulk oxide instead of those at oxide/GaAs interface. © 2007 American Institute of Physics.

[DOI: 10.1063/1.2798499]

The main obstacle to implement III-V compound semiconductors as novel channel materials for ultimate complementary metal-oxide-semiconductor (CMOS) applications is the lack of high-quality, thermodynamically stable insulators. Although in situ molecular beam expitaxy (MBE) Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) and ex situ atomic-layer-deposited (ALD) Al<sub>2</sub>O<sub>3</sub> show promising results, <sup>1-6</sup> a direct ALD HfO<sub>2</sub>, the high-k dielectric for Si CMOS at 45 nm node and beyond remains a challenge. Recently, Si (Refs. 7 and 8) or AlN (Ref. 9) surface passivation before HfO<sub>2</sub> deposition has been reported. Though improved C-V characteristics have been observed, these methods also have potential limitations. The Si interfacial layer could alter the doping concentration of the GaAs channel after subsequent high-temperature  $(T>750 \, ^{\circ}\text{C})$  processing required for dopant activation and degrade the channel mobility. The intrinsic thickness of an AlN layer can increase the effective oxide thickness. In this letter, we present a systematic interface study on ALD HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate gate dielectric on *n*- and *p*-type GaAs MOS devices, which combines the advantages of both Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>. More importantly, three major issues on compound semiconductor MOS C-V characterization, i.e., the "N-dispersion" phenomenon, inversion C-V, and the origin of hysteresis, are also insightfully discussed.

MOS capacitors were fabricated on both n- and p-type GaAs 2-in. substrates with doping concentrations of  $(4-6) \times 10^{17}/\text{cm}^3$ . After NH<sub>4</sub>OH based surface pretreatment, <sup>10</sup> 8 nm ALD Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> nanolaminate was deposited at 300 °C using an ASM F-120 ALD module. The nanolaminate contains alternate Al<sub>2</sub>O<sub>3</sub> (1 cycle) and HfO<sub>2</sub> (2 cycles) with Al<sub>2</sub>O<sub>3</sub> as the beginning layer. The Al<sub>2</sub>O<sub>3</sub> was deposited using trimethyl aluminum and water, and HfO<sub>2</sub> was deposited using HfCl<sub>4</sub> and water. For control samples, 8 nm ALD pure HfO<sub>2</sub> or pure Al<sub>2</sub>O<sub>3</sub> was also deposited at the same condition on GaAs substrates. Postdeposition annealing (PDA) was then conducted at 500 °C by rapid thermal annealing in N<sub>2</sub> ambient for 15 s, followed by electron beam evaporated Ni/Au metal as the gate electrodes. The leakage

current was measured using an HP4156A semiconductor parameter analyzer, and the capacitance was measured using an HP4284A precision *LCR* meter with frequencies varying from 1 KHz to 1 MHz. Similar experiments with (NH<sub>4</sub>)<sub>2</sub>S passivation were also performed. Negligible difference was found on *C-V* results, compared to those from NH<sub>4</sub>OH passivation.<sup>10</sup> The NH<sub>4</sub>OH passivation has certain advantages, viz., well understood chemical handling and a lack of potential sulfur contamination for CMOS manufacture lines. The *C-V* results presented in this letter are all obtained from NH<sub>4</sub>OH pretreatment.

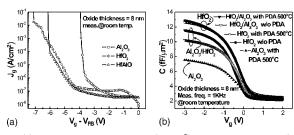

Figure 1(a) shows the gate leakage current density of p-GaAs MOS capacitors with HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate, HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics both after 500 °C PDA. The HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> laminate dielectric films exhibit lower leakage current and higher breakdown voltage than pure HfO<sub>2</sub> films. The gate leakage current density at 3 V gate bias is about  $6 \times 10^{-8} \text{ A/cm}^2$  for nanolaminate MOS and  $3 \times 10^{-7}$ A/cm<sup>2</sup> for pure HfO<sub>2</sub> samples. Meanwhile, the breakdown voltage is 6.1 V for nanolaminate samples, 3.8 V for pure HfO<sub>2</sub> samples, and 7.0 V for pure Al<sub>2</sub>O<sub>3</sub> samples. This corresponds to maximum electric strength of 7.9 MV/cm for nanolaminates, 5.0 MV/cm for HfO<sub>2</sub>, and 9.0 MV/cm for Al<sub>2</sub>O<sub>3</sub> after considering the difference between the metal work function and Fermi level of p-GaAs. The larger leakage current in HfO2 devices may be attributed to the creation of more leakage paths around crystallized grains formed from/ within the amorphous films after high temperature

FIG. 1. (a) Leakage current density  $J_g$  (A/cm²) vs gate bias  $V_g - V_{FB}$  (V) on HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate, pure HfO<sub>2</sub>, and pure Al<sub>2</sub>O<sub>3</sub> MOS capacitors after postdeposition annealing at 500 °C. (b) C-V characteristics of HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminate, pure HfO<sub>2</sub>, and pure Al<sub>2</sub>O<sub>3</sub> MOS capacitors before and after PDA process.

a) Author to whom correspondence should be addressed. Electronic mail: yep@purdue.edu

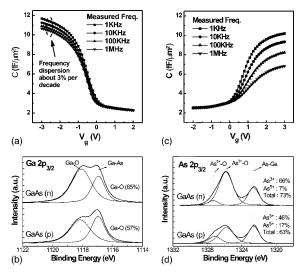

FIG. 2. C-V characteristics of  $HfO_2/Al_2O_3$  nanolaminate MOS capacitors measured at different frequencies ranging from 1 KHz to 1 MHz on (a) p-type GaAs substrate and (b) n-type GaAs substrate. The Ga  $2p_{3/2}$  (c) and As  $2p_{3/2}$  (d) core level peaks were obtained from p-GaAs and n-GaAs with native oxides. The contributions of Ga–O,  $As^{5+}$ –O, and  $As^{3+}$ –O were calculated after curve fitting assuming Gaussian-Lorentzian line shape.

annealing. 11,12 The insertion of intermediate Al2O3 layers effectively suppresses further HfO<sub>2</sub> crystallization and reduces the leakage paths in  $HfO_2$ . Figure 1(b) shows the C-V characteristics of HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> metal-oxidesemiconductor (MOS) capacitor (MOSCAP) before and after PDA, as well as Al<sub>2</sub>O<sub>3</sub> MOSCAP after PDA. The nanolaminate C-V shows significant enhancement after PDA. It has a sharper transition from the depletion region to the accumulation region than that obtained without annealing, indicating the improved interface quality. Additionally, the accumulation capacitance ( $C_{\text{max}}$ ) value is increased by ~15% after PDA and more than 50% higher than Al<sub>2</sub>O<sub>3</sub> with the same thickness. In contrast, HfO<sub>2</sub> MOS samples do not show an obvious difference before and after PDA. Notice that the capacitance value of nanolaminate structure is only about 10% lower than HfO2, while the breakdown voltage is almost doubled. The dielectric constant of the nanolaminates is  $\sim$ 12.5 deduced from the measured  $C_{\text{max}}$ , calculated semiconductor capacitance in GaAs, the area of the capacitor, and the film thickness. The midgap interface trap density  $(D_{it})$  is estimated to be around  $2 \times 10^{11}$ /cm<sup>2</sup> eV by the Terman method.

The frequency dispersion on accumulation capacitance is another important issue for high-k dielectrics on III-V. This dispersion could be as large as 50% or more on n-GaAs in the frequency ranging from 1 kHz to 1 MHz, which implies high interface trap densities at the conduction band edge of GaAs. Figure 2 summarizes the *C-V* characteristic measured on 500 °C annealed nanolaminate samples in the frequency range from 1 KHz up to 1 MHz. The frequency dispersion is about 3% per decade at this frequency range on the p-type GaAs substrate. Though the C-V curve still shows obvious modulation up to 1 MHz, the frequency dispersion is much more pronounced on the *n*-type GaAs substrate. This N-dispersion phenomenon is widely observed in our experiments with various oxides such as ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Ga<sub>2</sub>O<sub>3</sub>, and their combinations. Interestingly, this effect could also be found in literature without any special notice on this phenomenon.  $^{13,14}$  In many cases, only C-V curves on p-type GaAs are presented. 10,15,16

Although GaAs MOS research started as early as in 1965 at the RCA laboratory, <sup>17</sup> there are just a few reports in literature addressing the fundamental surface chemistry and physics on the difficult type of GaAs substrates. 18-21 Pashley et al. applied scanning tunnel microscopy to characterize the electronic properties of MBE grown GaAs (001) surfaces with  $(2\times4)/c(2\times8)$  reconstructions in high vacuum and found that Fermi level in p-GaAs is located near the valence band edge, in contrast to the midgap Fermi-level pinning in n-GaAs case due to the high density of acceptorlike kink sites formed at the surface of n-GaAs. Other experiments also indicate that p-GaAs has reduced surface state density, compared to n-GaAs, even after being exposed to air. <sup>21</sup> In order to understand this N-dispersion phenomenon with the current ex situ ALD process, we examine the composition of native oxides on *n*-type GaAs and *p*-type GaAs substrates by x-ray photoelectron spectroscopy (XPS), as shown in Figs. 2(c) and 2(d). The native oxide contributions to the Ga  $2p_{3/2}$ and As  $2p_{3/2}$  peaks, which are marked as Ga-O, As<sup>5+</sup>-O, and  $As^{3+}$ -O, are higher in *n*-GaAs than those in *p*-GaAs. Photochemical reactions on GaAs can explain why n-GaAs are oxidized easier than p-type GaAs. For illuminated *n*-GaAs, the reaction is GaAs+ $6e^+ \leftrightarrow Ga^{3+} + As^{3+}$ , which leads to photo-oxidation, i.e., Ga and As oxides and elemental As. In illuminated p-GaAs, the electron minority carriers result in surface passivation and the reaction is GaAs  $+3e^- \leftrightarrow Ga + As^{3-}$  and  $As^{3-} + 3H^+ \leftrightarrow AsH_3 \uparrow$ , which leads to preferential Ga oxide formation. Preferential Ga-O formation has also been previously reported in the case of O2 adsorption<sup>22</sup> as well as NH<sub>4</sub>OH-treated surfaces.<sup>23</sup> Although unpinning of the Fermi level of GaAs using ALD high-k dielectric is mainly due to the appropriate surface pretreatment<sup>3-5,10</sup> and the ALD "self-cleaning" process, <sup>14,24</sup> some may argue that a submonolayer amount of As-O species based on the above surface chemistry might exhibit more on n-GaAs than p-GaAs during the ex situ ALD process. This leads to larger interface density states at the conduction band edge and larger frequency dispersion observed on accumulation capacitance of *n*-GaAs.

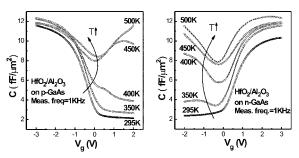

According to the Shockley-Read-Hall statistics and the low intrinsic carrier concentration  $(n_i)$  of  $10^6/\text{cm}^3$  in GaAs, the expected ac frequency to observe inversion C-V in dark and at room temperature is very low ( $\sim 0.002 \text{ Hz}$ ). Some observed that the "inversion-like" C-V curves at a few hundred hertz or up in GaAs could simply be due to the heavymetal (i.e., Ni, Fe, Zn, etc.) contaminated interface. The inversion feature diminishes after appropriate surface cleaning before dielectric deposition, i.e., HCl and H<sub>2</sub>O<sub>2</sub> based cleaning. The condition for reliable quasistatic C-V measurements with leakage current density of less than 10<sup>-8</sup> A/cm<sup>2</sup> is also hard to fulfill on ultrathin high-k dielectrics. Three approaches  $^{20}$  are recommended to study inversion C-V on III-V in general: (i) inversion-type MOS field-effect transistor with implanted source and drain, where minority carriers could be low-injected into the surface channel, (ii) photoillumination to increase the minority carrier concentration, and (iii) elevated temperature to increase the recombinationgeneration rates of minority carriers in GaAs. Figure 3 shows C-V curves on p-GaAs and n-GaAs taken at temperatures from 300 to 500 K. Depletion capacitances start to increase as temperature goes up to 400 K with full inversion at 500 K. The results demonstrate that Fermi-level unpinning is realized in these ALD nanolaminate GaAs MOS devices.

FIG. 3. C-V characteristics of  $HfO_2/Al_2O_3$  nanolaminate MOS capacitors measured at different temperatures ranging from room temperature to 500 K on (a) p-type GaAs substrate and (b) n-type GaAs substrate.

The temperature dependence of accumulation capacitance is explained by the so-called Goswami and Goswami's model. <sup>27</sup> According to this model, the measured series capacitance  $C_s$  is given by the relationship of  $C_s = C^* + 1/(\omega^2 R^2 C^*)$ , where  $C^*$  is the intrinsic capacitance. The increase in capacitance with increasing temperature is predicted by this model, providing that the resistance of dielectric R is thermally activated, with  $R = R_0 \exp(\Delta E/kT)$ . Here,  $R_0$  is a constant and  $\Delta E$  is the activation energy.

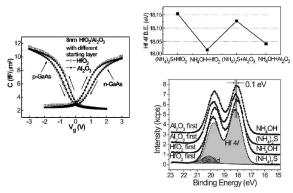

To further explore the influence of the presence of HfO<sub>2</sub> in the gate dielectric stack, experiments with different starting dielectric layers are conducted. The devices were fabricated on the same GaAs substrates with 5 cycles of Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub> as the starting layers followed by 8 nm Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> as the whole gate dielectric stack. The Al<sub>2</sub>O<sub>3</sub>-starting and HfO<sub>2</sub>-starting nanolaminate MOS devices have the same dielectric thickness, as well as annealing conditions. The C-V curves shown in Fig. 4(a) are surprisingly similar with negligible dependence on the starting layers. This demonstrates that the significant hysteresis (0.3-0.4 V) observed here are mainly from the mobile charges and traps in bulk oxide induced by HfO2 instead of those at oxide/GaAs interface. The results are consistent with the general observation that Al<sub>2</sub>O<sub>3</sub> films have much smaller hysteresis (~0.1 V) than HfO<sub>2</sub> films (0.5-0.6 V) and are roughly scaled with the film thicknesses. The above conclusion is also confirmed by XPS, as shown in Figs. 4(b) and 4(c). There is no observable difference on Al<sub>2</sub>O<sub>3</sub>-starting and HfO<sub>2</sub>-starting samples, though

FIG. 4. (a) 1 kHz bidirectional C-V characteristics of  $HfO_2/Al_2O_3$  nanolaminate MOS capacitors on both n-GaAs and p-GaAs with different starting layers. Curves with empty symbols are from  $HfO_2$ -starting samples and filled symbols are from  $Al_2O_3$ -starting laminate samples. No significant difference can be observed with different starting layers.  $HfO_2$ -starting samples have a little bit larger  $C_{\text{max}}$  as expected. High-resolution XPS analysis of Hf 4f peak (b) binding energy and (c) intensity on 3 nm  $HfO_2/Al_2O_3$  with  $NH_4OH$  or  $(NH_4)_2S$  different surface treatments and 5-cycle  $HfO_2$ -starting layer or  $Al_2O_3$ -starting layer.

Hf 4f and Al 2p (not shown) binding energy indicates a consistent (0.1 eV) chemical shift for the NH<sub>4</sub>OH treated surface relative to the (NH<sub>4</sub>)<sub>2</sub>S treated surface. The 2p sulfur band is below the detection limit of XPS and may be suppressed due to attenuation of the photoelectron by the overlying layer.

In summary, we have systematically studied interface properties of ALD  $HfO_2/Al_2O_3$  nanolaminate dielectrics on n- and p-type GaAs-MOS capacitors. A high dielectric constant and electric field strength, as well as inversion C-V characteristics at elevated temperatures is achieved by using this nanolaminate gate stack. The observed hysteresis is determined mainly from the mobile charges and traps in the bulk oxide induced by  $HfO_2$  instead of those at oxide/GaAs interface.

The work is supported in part by NSF (Grant No. ECS-0621949) and the SRC MARCO MSD Focus Center.

<sup>1</sup>M. Passlack, M. Hong, and J. P. Mannaerts, Appl. Phys. Lett. **68**, 1099 (1996).

<sup>2</sup>M. Hong, J. Kwo, A. R. Korton, J. P. Mannaerts, and A. M. Sergent, Science **283**, 1897 (1999).

<sup>3</sup>P. D. Ye, G. D. Wilk, J. Kwo, B. Yang, H.-J. L. Gossmann, M. Frei, S. N. G. Chu, J. P. Mannaerts, M. Sergent, M. Hong, K. Ng, and J. Bude, IEEE Electron Device Lett. **24**, 209 (2003).

<sup>4</sup>P. D. Ye, G. D. Wilk, B. Yang, J. Kwo, H.-J. L. Gossmann, S. N. G. Chu, S. Nakahara, H.-J. L. Gossmann, J. P. Mannaerts, M. Sergent, M. Hong, K. Ng, and J. Bude, Appl. Phys. Lett. **83**, 180 (2003).

<sup>5</sup>P. D. Ye, G. D. Wilk, B. Yang, J. Kwo, H.-J. L. Gossmann, M. Hong, K. Ng, and J. Bude, Appl. Phys. Lett. **84**, 434 (2004).

<sup>6</sup>K. Rajagopalan, J. Abrokwah, R. Droopad, and M. Passlack, IEEE Electron Device Lett. **27**, 959 (2006).

<sup>7</sup>S. Koveshnikov, W. Tsai, I. Ok, J. C. Lee, V. Torkanov, M. Yakimov, and S. Oktyabrsky, Appl. Phys. Lett. **88**, 22106 (2006).

<sup>8</sup>I. Ok, H. Kim, M. Zhang, T. Lee, F. Zhu, L. Yu, S. Koveshnikov, W. Tsai, V. Tokranov, M. Yakimov, S. Oktyabrsky, and J. C. Lee, Tech. Dig. - Int. Electron Devices Meet. **2006**, 346742.

<sup>9</sup>F. Gao, S. J. Lee, R. Li, S. J. Whang, S. Balakumar, D. Z. Chi, C. C. Kean, S. Vicknesh, C. H. Tung, and D.-L. Kwong, Tech. Dig. - Int. Electron Devices Meet. 2006, 346743.

<sup>10</sup>Y. Xuan, H. C. Lin, and P. D. Ye, IEEE Trans. Electron Devices **54**, 1811 (2007).

<sup>11</sup>G. D. Wilk and D. A. Muller, Appl. Phys. Lett. **83**, 3984 (2003).

H. Hu, S. J. Ding, H. F. Lim, C. X. Zhu, M. F. Li, S. J. Kim, X. F. Yu, J. H. Chen, Y. F. Yong, B. J. Cho, D. S. H. Chan, S. C. Rustagi, M. B. Yu, C. H. Tung, A. Y. Du, D. My, P. D. Foot, A. Chin, and D.-L. Kwong, Tech. Dig. - Int. Electron Devices Meet. 2003, 1269303.

<sup>13</sup>W. P. Li, Y. X. Liu, X. W. Wang, and T. P. Ma, Proceedings of the 36th IEEE Semiconductor Interface Specialists Conference, Washington DC, December 2005 (unpublished).

<sup>14</sup>M. L. Huang, Y. C. Chang, C. H. Chang, Y. J. Lee, P. Chang, J. Kwo, T. B. Wu, and M. Hong, Appl. Phys. Lett. 87, 252104 (2005).

<sup>15</sup>N. Goel, P. Majhi, C. O. Chui, W. Tsai, D. Choi, and J. S. Harris, Appl. Phys. Lett. **89**, 163517 (2006).

<sup>16</sup>M. Zhu, C. H. Tung, and Y. C. Yeo, Appl. Phys. Lett. **89**, 202903 (2006).

<sup>17</sup>H. Becke, R. Hall, and J. White, Solid-State Electron. **8**, 813 (1965).

18X. Yin, H.-M. Chen, F. H. Pollak, Y. Cao, P. A. Montano, P. D. Kirchner,

G. D. Pettit, and J. M. Woodall, J. Vac. Sci. Technol. A 10, 131 (1992).

19T. H. Pollak, L. Vac. Sci. Technol. B, 11, 1710 (1992).

<sup>19</sup>F. H. Pallak, J. Vac. Sci. Technol. B **11**, 1710 (1993).

<sup>20</sup>M. D. Pashley, K. W. Haberern, R. M. Feenstra, and P. D. Kirchner, Phys. Rev. B 48, 4612 (1993).

<sup>21</sup>D. Yan, E. Look, X. Yin, F. H. Pollak, and J. M. Woodall, Appl. Phys. Lett. **65**, 186 (1994).

<sup>22</sup>P. Kruse, J. G. McLean, and A. C. Kummel, J. Chem. Phys. **113**, 9217 (2000)

<sup>23</sup>M. V. Lebedev, D. Ensling, R. Hunger, T. Mayer, and W. Jaegermann, Appl. Surf. Sci. 229, 226 (2004).

<sup>24</sup>M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul, and D. A. Muller, Appl. Phys. Lett. 86, 152904 (2005).

<sup>25</sup>S. R. Hofstein and G. Warfield, Solid-State Electron. **8**, 321 (1965).

<sup>26</sup>Y. Xuan, H. C. Lin, and P. D. Ye, ECS Trans. **3**, 59 (2006).

<sup>27</sup>S. A. Awan and R. D. Gould, Thin Solid Films **423**, 267 (2003).